Zephyr RTOS and RISC-V: Enabling Next-Gen Edge FPGA Devices

The drive for real-time intelligence at the edge is revolutionizing device design and deployment in today’s quickly changing embedded environment. Modern applications, such as sensor-driven IoT networks and smart production floors, require computing platforms that are not only effective but also scalable and flexible. Open-source, modular solutions are becoming more popular because of traditional designs’ frequent limitations due to proprietary and inflexible functionality. This blog examines how next-generation edge computing systems that satisfy the increasing demand for performance, adaptability, and creativity in embedded applications are made possible by the combination of Zephyr RTOS and RISC-V with FPGA platforms.

RISC-V permits scalable processor cores without licensing restrictions. It is particularly appropriate for edge devices. It offers a flexible architecture that supports peripherals and manages multiple tasks, enabling edge communication and real-time data processing when coupled with Zephyr RTOS. This blog explores how the collaboration of Zephyr RTOS and RISC-V on Lattice FPGA affects edge computing with practical use cases and architectural concepts.

Why RISC-V and Zephyr RTOS for Edge FPGA Devices?

The demand for adaptable, effective, and flexible embedded systems has increased as edge computing becomes an essential part of industrial automation, the Internet of Things, and real-time data analysis. This is where Zephyr RTOS and RISC-V work together to great advantage. Despite being constrained by proprietary designs, developers can create application-specific processing cores using RISC-V, an open and extensible Instruction Set Architecture (ISA). For edge deployments using FPGAs, their modular layout is perfect for maximizing performance, minimizing silicon expansion, and attaining energy efficiency.

The combination of Zephyr RTOS and RISC-V makes for an attractive option for next-generation edge FPGA devices. Without sacrificing performance, they support edge applications that require low power consumption, modular upgradability, and real-time responsiveness. Designers can tweak hardware and software layers for specific applications such as edge gateways, industrial controls, or smart sensors with this synergy. Both platforms are ideal for businesses looking to future-proof their embedded edge systems by supporting open-source ecosystems, cutting development cycles, fostering creativity, and reducing licensing costs.

Let us see how RISC-V and Zaphyr RTOS function on a Lattice FPGA:

Architectural Design: Temperature Monitoring with RISC-V on Lattice FPGA

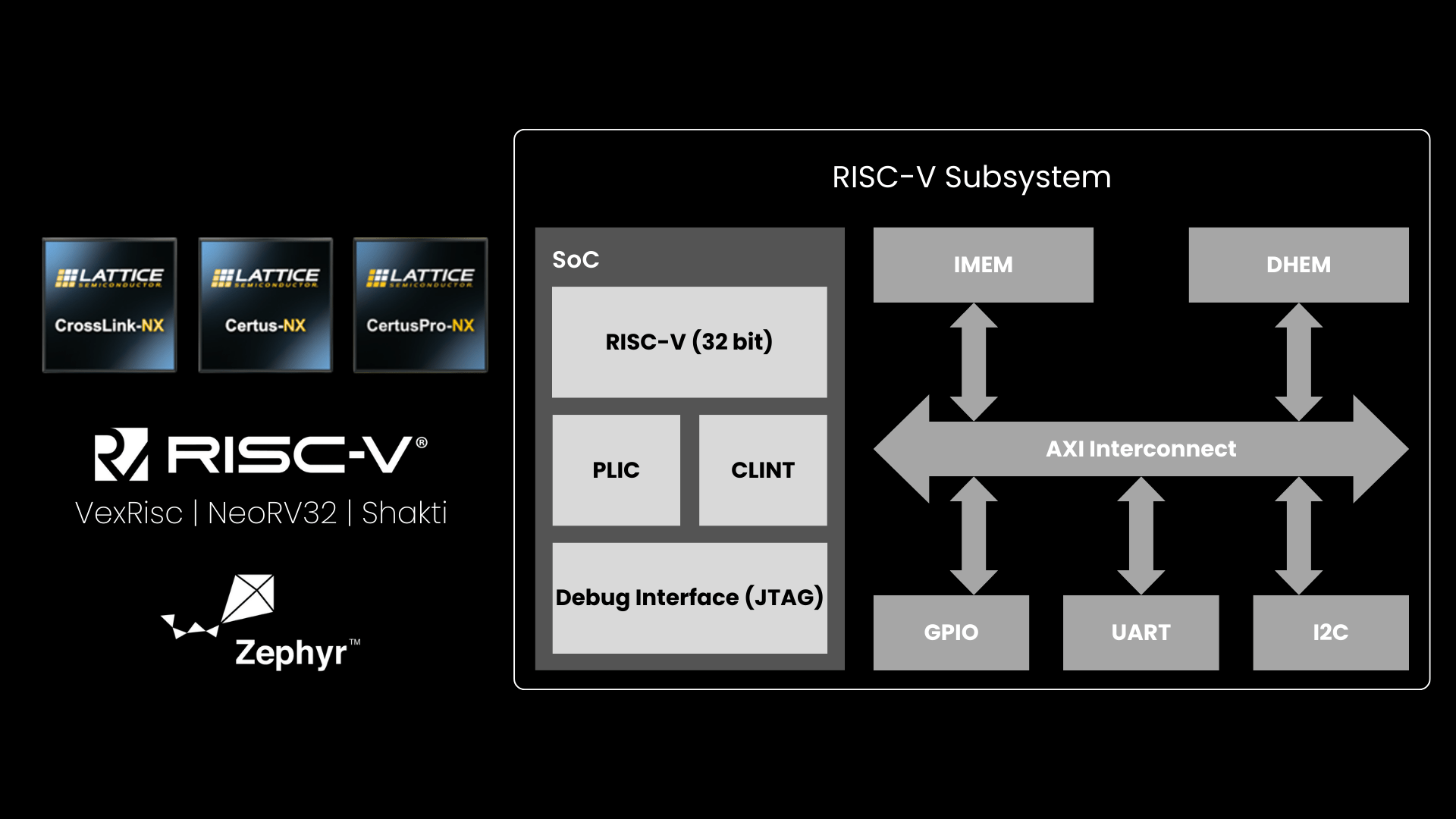

A solid architecture implementation of a custom 32-bit RISC-V core (RV32IMA) integrated with Zephyr RTOS on Lattice FPGA platforms. Operated at 100 MHz, the core employs on-chip instruction memory (IMEM) and data memory (DMEM) and enhances performance with cache for instruction and data fetching.

The core further contains the CLINT (Core Local Interrupt Timer) and PLIC (Platform-Level Interrupt Controller) for timely timer and interrupt management. Standard embedded peripherals like GPIO, I2C, UART are included to enable complete system I/Os, whereas JTAG debugs on-chip for real-time I/O.

This modularizable and extensible architecture is realized using Zephyr RTOS to create a real-time and multitasking environment tailored for edge applications. As a real-world use case, a temperature monitoring system was developed, which used scheduled activities and interrupt-driven processes to drive sensor data when it was read over I2C. The predictable nature and small footprint of the RTOS were demonstrated by Zephyr’s ability to multitask through real-time temperature monitoring, processing inputs from external events, and a few predefined periodic functions.

Together, this RISC-V + Zephyr RTOS system on FPGA demonstrates how developers can build scalable, flexible, and power-efficient embedded platforms while leveraging the strength of open-source ecosystems for faster innovation and deployment at the edge.

System Architecture Overview

1. Components Breakdown:

- Customized RISC-V Processor Core

Being a 32-bit core RV32IMA for embedded applications, this core is light in size and power; it efficiently deals with processing. It consists of integer arithmetic and atomic operation support, hence the possibility of soft-core implementation over Lattice FPGAs. - Zephyr RTOS Layer

This is a light real-time operating system that provides a deterministic, multitasking, event-handling, and low-latency scheduling mechanism. It allows modular driver integration, thread prioritization, and efficient resource management on constrained hardware.

- Peripheral I/O Interfaces (GPIO, UART, I2C)

When used for the control and monitoring of external devices in digital fashion, GPIO implements UART and I2C serial communication. These standard interfaces provide the backbone for expanding peripheral connections with sensors, actuators, and intercommunication between devices.

- Memory + Cache Configuration (IMEM, DMEM)

IMEM (Instruction Memory) and DMEM (Data Memory) are on-chip blocks that are designed for minimal power consumption and quick retrieval. By reducing memory latency during instruction collection along with information access, cache integration enhances performance.

- JTAG Debugger Interface

JTAG-compatible interface is embedded to support real-time debugging, setting of breakpoints, and permit access to hardware traces, allowing the connection to the processor trace probes while halting it. This allows seamless hardware-software co-verification during firmware development and system bring-up.

Best Practices for Building Embedded Edge FPGA Systems

1. Leverage Open-Source Ecosystems (RISC-V + Zephyr)

- Use Open-source technology such as RISC-V and Zephyr RTOS to reduce time-to-market through easily accessible IP cores, driver libraries, and modules contributed by the communities. Promote vendor independence as well as reduce development costs by not having to pay for the licensing associated with proprietary formats.

- Completely customizable architectures permit rapid adjustment from the widest embedded use cases to the largest hardware platforms.

2. Maximize Core and RTOS Customization

- For power and space efficiencies on FPGAs, adapt the RISC-V instruction set to include just the functional blocks required by the application.

- The Kconfig-based building system of Zephyr makes it very selective on including OS features, kernel services, and peripheral drivers. This reduces to very light and maintainable firmware while drastically improving performance.

3. Optimize Peripheral Integration for Scalability

- Efficient interfacing of standard peripherals like GPIO, UART, and I2C with memory-mapped or bus-based protocols (like AXI, APB) for large-scale I/O coverage.

- Encapsulating hardware abstraction into modular design within the Zephyr device tree for reuse across several platforms.

- This allows easy scaling of the design to handle more complex systems and long peripheral sets.

4. Build a Robust Debugging Infrastructure

- On-chip JTAG-compliant debug modules that allow for non-intrusive real-time firmware inspection, breakpoint control, and trace logging.

- Also allow easy integration to open-source tools, like OpenOCD, as well as vendor-specific IDEs, such that hardware-software co-debugging is fully enabled.

- Saves lots of development time and makes fault isolation easy during system bring-up.

5. Enable Support for Multi-Core, Future-Ready Workloads

- Architect the RISC-V subsystem to include provisions for symmetric or asymmetric multi-core configurations to support parallel execution paths.

- Employ Zephyr’s SMP or AMP capabilities to manage the inter-core communication and task scheduling of heterogeneous environments.

Such a technique assures that the architecture remains forward compatible by anticipating workloads, such as edge AI, sensor fusion, and secure networking, as they enter the foreground of consideration.

Industrial Use Cases of Zephyr RTOS and RISC-V Integration

- Industrial Automation Controllers

Critical real-time performance and reliability in industrial automation applications will dictate the future of Zephyr RTOS, combined with a custom RISC-V core on an FPGA to enable deterministic control under low power usage with interesting hardware flexibility. Task scheduling is accurate under Zephyr, while reconfigurable logic by the FPGA addresses retrofitting for future needs—this will be the mark of intelligent controllers for Industry 4.0.

- IoT Edge Gateways

IoT edge gateways locally handle sensor data, processing and filtering it before transmission to the cloud. For real-time decision making, data security, low lag in processing, deterministic control, and integration with dynamic protocols, they are employing the Zephyr real-time operating system on its custom RISC-V core in an FPGA. So, the efficient and adaptable edge gateway solution is created.

Industrial Use Cases of Zephyr RTOS and RISC-V Integration

- Smart Sensors and Wearable Devices

Smart sensors and wearable devices require fast data processing, low power consumption, and small size. Using Zephyr RTOS on a custom RISC-V core in an FPGA keeps systems lightweight and predictable. The sensor data can be evaluated in real-time using this setup. The FPGA offers flexibility when designing custom interfaces, while Zephyr is employed for accurate task scheduling. Such systems are well-suited for factory safety instruments, fitness gadgets, and health monitoring tools.

All in all, combining Zephyr RTOS and RISC-V on FPGA platforms offers a robust foundation for developing low-power, real-time, and scalable edge systems. A custom 32-bit RISC-V core running Zephyr, demonstrated across multiple Lattice FPGAs, highlights real-time capabilities such as event handling and task scheduling. The modular architecture with integrated peripherals ensures adaptability for diverse industrial and IoT applications.

As a partner of Lattice Semiconductor, MosChip brings deep expertise across multiple Lattice FPGA platforms. Leveraging its proven capabilities in product engineering services across diverse platforms, processors, operating systems, architectures involving RISC-V, and interfaces, MosChip delivers customized, scalable and small form factor edge solutions for various industrial domains with accelerated time-to-market.

To know more about MosChip’s capabilities, drop us a line, and our team will get back to you.

Author

-

Jigarkumar Mori is a Senior Manager in FPGA/ RTL Design at MosChip. He has 13 years of experience specializing in FPGA, RTL design, VHDL, Verilog, MATLAB, Simulink, computer vision, and deep learning development. As a skilled engineer, he has developed expertise in designing and implementing Xilinx and Lattice FPGA-based systems, as well as programming languages such as VHDL and Verilog, to optimize performance and efficiency. His proficiency in MATLAB and Simulink has allowed him to develop sophisticated algorithms and models, pushing the boundaries of what's possible in computer vision and deep learning applications.