25 years of revolution in silicon engineering and product engineering services from India to the world.

MosChip has more than 30+ IP digital in its portfolio. We provide digital verification IPs and validation services ranging from analog, mixed-signal, ASIC, SoC, digital logic, and custom IP. We use advanced verification methods for projects as per the client’s process.

USB3 Gen2 x2 link with fallback to Gen2 x1, Gen1 x2, Gen1 x1, and backward compatibility for USB2 High/Full Speed modes. Support PIPE and UTMI+/ULPI interfaces with full link power management

USB3 Gen2 x2 link with fallback to Gen2 x1, Gen1 x2, Gen1 x1, and backward compatibility for USB2 High/Full/Low Speed modes. Support PIPE and UTMI+/ULPI interfaces with full link power management. The clock domain crossing mechanism between USB and xHCI/system-bus logic provides flexibility for easy integration.

USB 3.2 Dual Role Device (DRD) softcore semiconductor IP is designed for applications requiring both USB Host and Device implementation. This core comprises USB3.2 SSP, SS, HS/FS/LS Host, and Device controllers in a single codebase that supports role-swap functionality

USB 3.2 Retimer softcore is designed for use in USB Port/Cable Retimer applications with USB SuperSpeed Plus/SuperSpeed link operations. The IP has been verified in simulation and is synthesis clean for FPGA implementations

The PCI Host controller offers a PCI 32-bit bus operating at 33MHz and supports PCI devices conforming to the PCI Local Bus Specification 2.1. PCI Host Bridge contains an internal arbiter to manage up to 4 external devices

SHA-1 IP core implements Secure Hash Algorithms specified in FIPS 180-4 standard. Common cores are available for ASIC and FPGA applications.

SHA3 IP is a high-throughput implementation of SHA-3 cryptographic hashing function built-in an area-efficient approach. The core can provide all the fixed-length hashing functions provided as part of the SHA-3 standard. A common core is available for diverse ASIC & FPGA applications. It ensures data integrity and/or user authentication in a range of applications, including IPsec and TLS/SSL protocol engines, encrypted data storage, secure processing systems, e-commerce, and financial transaction systems.

AES core implements the Rijndael algorithm for encryption and decryption of plain text using cipher keys. It is compliant with FIPS 197 standards. The core works with a pre-expanded key, or with optional key expansion logic. The encryption core accepts new plain text every 11 clocks. The decryption core accepts new cipher text after 22 clocks when using the new key and after 11 clocks when using a pre-expanded key

Reed Solomon IP core codec is based on IEEE 802.3bj Clause 91 specification. The cyclic code used is RS (528,514) for 7 symbol error correction and RS (544,514) for 15 symbol error correction. Encoder and Decoder are separate synthesizable cores. Different architectures are available to meet area and throughput requirements. RS-based IP cores are available for applications beyond IEEE 802.3bj.

Data-backup can push your costs up by 200%, and even there are high chances of data loss. Manage erasures and optimize your data recovery costs with an IP based on Reed-Solomon codes. Data erasure is a powerful way to tighten data security. Modern applications built for data centers and the cloud can make your organization vulnerable as storage devices have a high probability of being corrupted. While data-backup solutions are useful, they can push the costs up exuberantly. Why not get a smart solution that ensures 100% data recovery in case of up to certain storage device failures?

The Ethernet controller is compliant with IEEE802.3 and it provides an interface between the host subsystem and the Media Independent Interface (MII). The 10/100 Ethernet MAC consists of DMA (TX DMA, RX DMA), TLI (TX buffer, RX buffer), 10/100 Ethernet controller. The DMA automates data transfers and frees the CPU from this task. The Transaction Layer Interface (TLI) is a 64-bit wide block designed to provide a bridge between the DMA controller and a 10/100 Ethernet controller. The TLI uses 4 Kbytes FIFO for transmit (TX Buffer) and 2 Kbytes FIFO for receive (RX Buffer)

The Client is US based leading semiconductor company having expertise in…

The Client is US based leading semiconductor company having expertise in…

The Client is US based leading semiconductor company having expertise in…

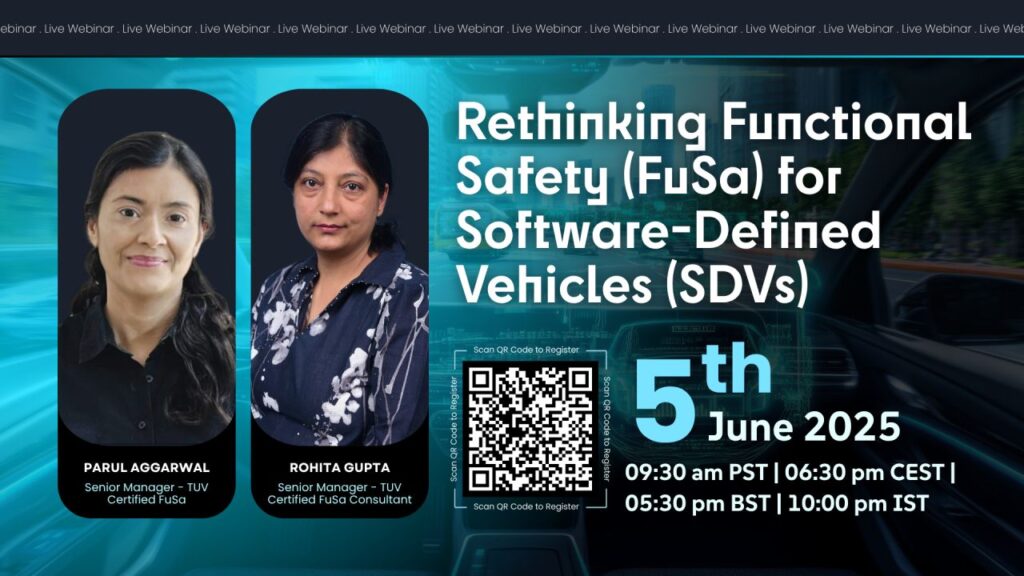

Upcoming Webinar: Rethinking Functional Safety [FuSa] for Software-Defined Vehicles [SDVs]

Upcoming Webinar: Rethinking Functional Safety [FuSa] for Software-Defined Vehicles [SDVs]