The client is a manufacturer of embedded hardware boards based in the United States. Their embedded boards are targeted to applications…

The client is a Europe-based semiconductor firm. They provide custom silicon solutions across different domains like automotive, consumer…

The client is a US-based company that offers immersive multimedia solutions. They provide next-generation media technology for automotive…

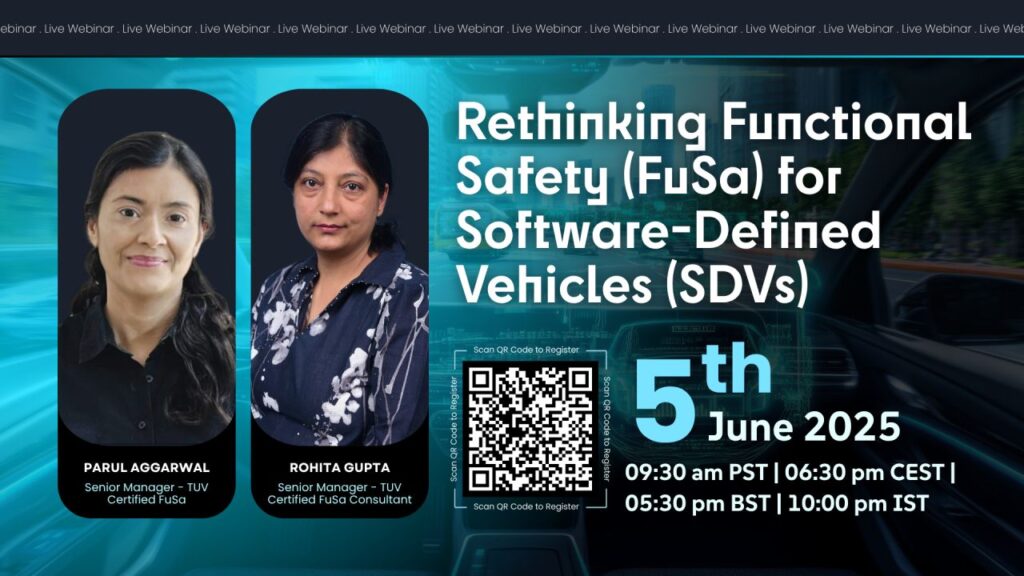

Recent Webinar: Rethinking Functional Safety [FuSa] for Software-Defined Vehicles [SDVs]

Recent Webinar: Rethinking Functional Safety [FuSa] for Software-Defined Vehicles [SDVs]