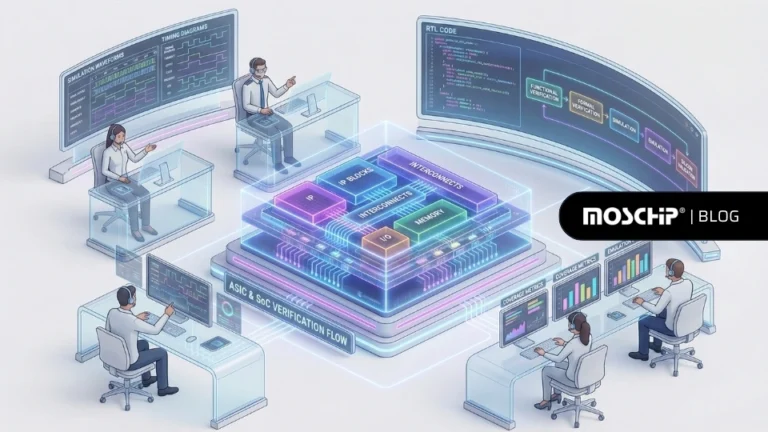

ASIC and SoC Verification: A Comprehensive Methodology Guide

ASIC and SoC verification is the engineering unit responsible for demonstrating that a hardware implementation conforms to its specification across all relevant operating conditions…

ASIC and SoC verification is the engineering unit responsible for demonstrating that a hardware implementation conforms to its specification across all relevant operating conditions…

Across semiconductor programs, one pattern continues to drain time, predictability, and momentum. Companies don’t fall behind because their architectures are too ambitious…

Know how we have helped our client get more safety rating for their latest auctomobiles launched!