### **CORPORATE OVERVIEW 2023**

CONNECTING THE WORLD

Silicon | Systems | Software | IoT

#### **OVERVIEW**

Established in 1999, with 20+ years of expertise Developed and shipped millions of connectivity ASICs over the years Focused on Product Engineering in Mixed signal IP, Turnkey ASICs, Semiconductor and IOT solutions 1300+ engineers spread across Silicon valley - USA, Hyderabad, Bangalore, Ahmedabad & Pune Domain expertise in IoT, Consumer, Multimedia, Automotive, Networking & Telecommunications, Handheld, Storage, Edge Applications

"We are one of the versatile organizations with solutions & services for almost every industry" - CEO

#### **BUSINESS UNITS**

#### **Semiconductors**

#### **Embedded System & Software Design**

#### **Semiconductor IP**

- Digital IP

- Verification IP

- SerDes IP

- ADC / DAC IP

- PLL IP

#### Semiconductor Design Services

- RTL design & verification

Services

- Analog layout services

- Physical design services

#### **Turn-key ASIC**

- RTL to Volume Production

- Working relationship with leading fabs

- Successful track record

### Product / System Design

- High Speed

Product &

System Design

- Platform

Designs with FPGA,

SoC & ASIC's

- DFM / DFA, & EMS

- Platform Bring-up & Validation

#### **Embedded Software**

- OS Porting & Board Support Package

- Device Drivers –

Bare metal, OS

- Software Integration

- Software Testing

- Software maintenance/ support

ISO 9001:2015 certification for SoC Design, Development, Assembly, Supply & Services of Semiconductors, Software & Systems

#### **LOCATIONS**

#### **TECHNOLOGY ALLIANCES**

**BUILD PARTNER**

5

www.moschip.com © Copyright

**Mentor**°

Click Here to View Details

#### FOUNDRY ALLIANCE - TSMC DCA PARTNER

"We're very pleased with the addition of MosChip to our OIP Design Center Alliance to address the growing market need for design services on TSMC's industry-leading technologies," said **Dan Kochpatcharin**, Head of the Design Infrastructure Management Division at TSMC. "Our partnership with MosChip expands TSMC's design ecosystem and enables our mutual customers to achieve next-generation design success and quickly launch their differentiated products to market."

# SEMICONDUCTOR IP

#### MIXED SIGNAL IP AND RELATED SERVICES

IP

#### **CUSTOMIZE**

#### **INTEGRATE**

### Mixed-Signal IP Standards Based IP

- PCIE Gen1/2/3 PHY

- SATA I/2 PHY

- XAUI PHY

- CEI-6G-SR-PHY

- SerialLite PHY & PCS

- ARM HSSTP PHY & Link

- PCIE Gen4 PHY (In Lab)

#### **Analog IP**

ADC, LVDS I/O, PLL

#### **Customer Specific:**

Custom SerDes for automobile / ADC / other applications  MosChip Technologies offers customization to other Foundries / nodes and emerging standards

#### Porting to other foundries

- TSMC, Global, Tower

- 180nm, 130nm, 55nm

40nm, 28nm, 22nm,

16FF, 14FF, 7FF, 6FF, 4FF,

5FF, 3FF

- MosChip technologies offers design services for customization / porting of customer's own technology

- MosChip Technologies offers complete integration services of their IP into customer's SOCs. In addition, MosChip Technologies' services division provides design services in the following:

- Synthesis

- DFT

- Place & Route

- Analog/Mixed Signal Design

- Analog Layout

#### **ANALOG IP CUSTOMIZATION SERVICES**

| Nodes                              |         |                   |  |

|------------------------------------|---------|-------------------|--|

| ТЅМС                               | SAMSUNG | GLOBAL<br>FOUNDRY |  |

| FinFET 3nm,<br>5nm, 6nm and<br>7nm | 4nm     | 12LP              |  |

| 12FFC                              | 5nm     | 14FF              |  |

| 28nm HPC,<br>HPC+                  | 12nm    | 22 FDX            |  |

| 40LP, 180nm                        |         | 40nm,<br>55nm     |  |

| CUSTOMER PROJECTS                   | INTERNAL PLATFORMS          |

|-------------------------------------|-----------------------------|

| DISPLAY PORT/HDMI<br>SerDes (10G)   | Long Range SerDes<br>(16G)  |

| Multi-<br>Protocol SerDes<br>(6.4G) | Short Range SerDes<br>(10G) |

| DDR4, GDDR5 PHY                     | ARM HSSTP PHY<br>(12.5G)    |

| TOUCH SENSOR<br>IMAGE SENSOR        | ADC                         |

| Serial Lite SerDes<br>(2.5G)        | LVDS IO, PLL                |

**Design Tools**

**Layout Tools**

**Other Tools**

cādence°

#### **50+ Engineers**

- Capable of providing Complex IPPorting solutions like Serdes, DDR

- Experience in working with Latest nodes in TSMC and Samsung

- Recognized TSMC Partner (TSMC DCA Partner)

- Adheres to strict IP Development

Methodology

- Follows established CAD Flows and Methodology

- Adherence to ISO Standards,

ISO9001:2015 Certified Company

- Professional Program

Management and Status

Updates

#### **MOSCHIP SERDES IP**

#### [Phy product standards' overview]

| Name                 | Standards             | PCS         | Data Rate per Lane (Gbps)         | Comments                                                                                                                       |

|----------------------|-----------------------|-------------|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| PCIe Gen 1           | PCIe 1.1              | PIPE        | 2.5                               | <ul> <li>Endpoint or Root Complex</li> <li>PIPE includes skip insertion, deletion</li> <li>PCle power savings modes</li> </ul> |

|                      | PCIe 1.1              | PIPE        | 2.5                               | Endpoint or Root Complex                                                                                                       |

| PCIe Gen 2           | PCIe 2.1              | PIPE        | 5.0                               | <ul> <li>PIPE includes skip insertion, deletion</li> <li>PCle power savings modes</li> <li>Port bifurcation support</li> </ul> |

| PCIe Gen 3           | PCle 3.1/2.1/1.1      | Partners    | 8.0                               | <ul><li>Endpoint or Root Complex</li><li>PCle standard multi-lane interface</li></ul>                                          |

| XAUI                 | XAUI, CX4, KX4        | Customer    | 2.4 - 3.2 / 1.2 - 1.6             | Generic backplane uses                                                                                                         |

| CEI-6                | CEI-6, XAUI, CX4, KX4 | Customer    | 4.8 - 6.4 / 2.4 - 3.2 / 1.2 - 1.6 | Generic backplane uses                                                                                                         |

| SATA I/II/III        | SATA I/II             | SATA        | 1.5/3.0                           | <ul> <li>Advanced frequency offset (PPM) compensation for +0 / -0.5%</li> </ul>                                                |

| SATA IJIIJIII        | SATA III              | SATA        | 6.0                               | SSC                                                                                                                            |

| Switchable           | Multiple              | Multiple    | Multiple                          | <ul><li>Switchable between 2 or 3 standards</li><li>Separate interface for each standard</li></ul>                             |

| ARM HSSTP            | HSSTP 6.0             | Aurora Link | 6.25 / 12.5                       | ARM HSSTP PHY along with Link Layer as a single macro                                                                          |

| PCIe Gen4            | PCIe 4.0              | Partners    | 16                                | Test silicon functional and in CHAR/Debug                                                                                      |

| Seriallite PHY       | IEEE149.1             | PCS         | 3.125                             | chip2chip, board2board, shelf2shelf or backplane                                                                               |

| 10/100/1000 Ethernet | IEEE802.3             | PCS         | 1                                 | AFE Block in development                                                                                                       |

| USR/VSR/SR           |                       | PCS         | 10                                | Chip to Chip SerDes. In Development                                                                                            |

#### **MOSCHIP DIGITAL IP**

#### **USB**

- Host Controller

- Device Controller

- Retimer

- Dual-Role-Device

#### **SECURITY**

- Secure Hash Algorithms (SHA1, SHA2, SHA3)

- Reed-Solomon based FEC

- Reed-Solomon based Erasure (Static & Dynamic)

#### **ENCRYPTION**

- Advanced

Encryption

Standard (AES 128,

AES 256)

- XTS-AES

Best in class performance

Up to 20% Better throughput

Platform Independent

# SEMICONDUCTOR DESIGN SERVICES

#### **OVERVIEW OF SEMICONDUCTOR GROUP**

- Achieved "first-pass silicon success" across 400+ tape-outs

- Expertise ranging from 500nm to the latest 3/5/6/7 /10 /14 /16 nm FinFET & SOI process nodes

- Very strong RTL Design, Design Verification, Physical Design, Analog Design, and Analog Layout team with over 15 years of average experience in the senior team

- Engaged in complex chip designs extending to 100+ million gates

- Highest level of training & experience on state-of-the-art technologies

- Design Houses in Hyderabad, Bengaluru, Ahmedabad, Pune and Santa Clara, USA

900+ VLSI Engineers

400+ Tape-outs with 100% First-Pass Silicon Success

Engagement Model ODC | T&M | Turnkey

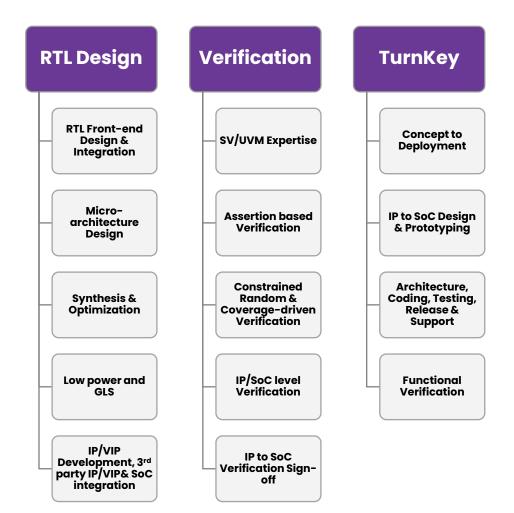

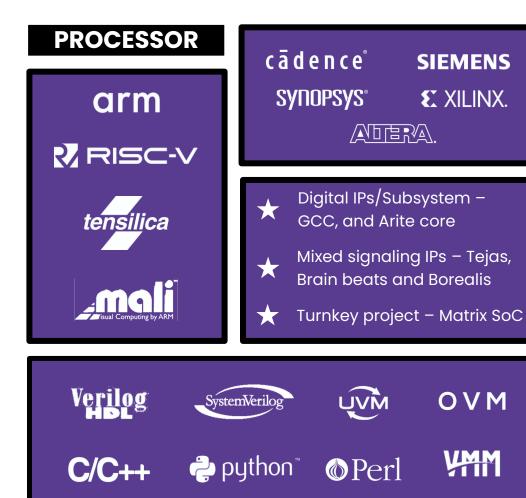

# RTL DESIGN & DESIGN VERIFICATION SERVICES

18+ AVG.EXP. OF LEADERSHIP 100+ TAPE-OUTS 200+ ENGINEERS

TOOLS

**HIGHLIGHTS**

LANGUAGES

#### **RTL DESIGN & VERIFICATION**

#### **TECHNOLOGY EXPERTISE**

#### IP Interfaces / Protocols

#### Ethernet

HDMI | SATA

SAS | CAN

AXI/APB

XHCI | PIPE

UTMI+ULPI

SPI | I2C

Interlaken

MIPI | DP

#### Verification Tools

Questa | Incisive

VCS | Jasper

QuestaFormal

Xcellium

Simvision

Visualizer

Codelink Verdi

Formality

FormalPro

QuestaSLEC

Conformal

### Languages & Methodology

#### Scripts

#### Prototype Platforms

# ANALOG LAYOUT SERVICES

18+ AVG.EXP. OF LEADERSHIP

150+ TAPE-OUTS 250+ ENGINEERS

#### **Technologies**

- TSMC N3E | N3P | 5FF | 6FF | 7FF | 12FF | 16FF

- TSMC 22nm, 28nm, 180nm

- SAMSUNG 3nm, 4nm, 5nm, 7nm

- GF 14nm, 12nm, 22nm, 40nm, 55nm, 65nm

#### **Expertise**

- High Speed Serdes up to 112Gbps Very Short Reach or Extra Short Reach Serdes of 112Gbps data rate, PCle6 Gen Protocols

- Power Management Layouts LDO, BGR, SMPS, Bias blocks, Buck Boost converters, etc.

- I/O cells GPIOs, LVDS, DDR Ios and GDDR IOs

- Data Converters ADC, DAC with different architectures (Pipeline, SAR ADC, Flash ADC, Current steering DAC and R-2R ladder DAC)

- RF Layouts

- Memory Layouts Register files, Dense RAM, Cache Memory, CAM Memory

- Clock Generators Phase Locked Loop, Delay Locked Loop

# NVEILING

Ready to Tape-out the Chip in 3nm

\*

TSMC 22nm Ultra Low Leakage (ULL) AIOT Edge AI SoC for NTU, ASTAR & EMass.ai [RTL-Silicon]

# LOOLS

cādence° GMenter

Ansys SYNOPSYS°

# нісніснтѕ

- ★ SerDes Up-to 112GBPS

- SerDes PCLe5 & PCLe4 with Multiprotocol support

- ★ SerDes Up-to 112GBPS

#### **ANALOG LAYOUT - IP DETAILS**

| PRODUCT                    | TECHNOLOGY  | SPECIFICATION              | APPLICATION                                               |

|----------------------------|-------------|----------------------------|-----------------------------------------------------------|

| XSR SerDes                 | TSMC N5     | 112 Gbps                   | Networking/Servers                                        |

| PCIe Gen6                  | TSMC N5     | 64 Gbps                    | Networking / Servers                                      |

| DDRIO                      | TSMC N3     | 4.8 Gbps - 5.6 Gbps        | Memory Applications                                       |

| DDRIO                      | TSMC 5G     | 4.8 Gbps - 5.6 Gbps        | Memory Applications                                       |

| DDRIO                      | Samsung 5nm | 4.8 Gbps - 5.6 Gbps        | Memory Applications                                       |

| Graphical DDR              | TSMC 12FFC  | 12 Gbps                    | Memory Applications                                       |

| PMU / PMW Controllers      | TSMC180     |                            | Laptop / Servers                                          |

| High Precision Oscillators | TSMC N55    | Speed of 5Ghz              | Aerospace, Defense, Automotive, Electronics, Mobile & IoT |

| Clock Generator            | TSMC N3     | Speed of 5Ghz              | Processors                                                |

| Smart Electrical Meter IC  | TSMC 180    | 45-55Hz, 1 Phase / 3 Phase | Electric Measuring Applications                           |

# PHYSICAL DESIGN SERVICES

20+ AVG.EXP. OF LEADERSHIP 150+ TAPE-OUTS 400+ ENGINEERS

#### PHYSICAL DESIGN SERVICES

#### **EXPERTISE**

- Block-Level Place & route

- Timing Closure & Static Timing Analysis

- Multiple Domain Clock-Tree Synthesis

- Physical Verification (DRC/ERC/LVS)

- EM-IR Drop Analysis, SI Closure

- Chip-Integration

- Logic Synthesis & Physical Synthesis

- Low Power Expertise Clock Gating, Multi-Vt, Voltage Islands, Power Gating

#### **FLIP-CHIP EXPERTISE**

- O-ring design

- Bump Assignment work with Package team and Finalize

- Customer Designed Bump/RDL integration to chip level

- RDL Design and Routing

- Help Customers to decide Metal Stack

- Bumps and Package

LEADERSHIP HISTORY

#### **HIGHLIGHTS**

- Full-Chip Integration | Floor-Plan | Analog Integration | IP-Integration

- Full-Chip Pin-Assignment & Budgeting | Power-Grid Design & Analysis

- Clock-Design | timing Closure | Physical Verification & EM-IR

- DDR-Integration using new generation timing libraries (LVF)

#### **TOOLS**

cādence<sup>®</sup>

SIEMENS

SУПОРЅУЅ<sup>®</sup>

GMentor

# SUMMARY OF RECENT & RELEVANT SAMPLE PD PROJECTS

| PROCESS         | APPLICATION | DESIGN FEATURES                 | TEAM SIZE<br>PD ENGINEERS | FLOW     | DURATION<br>MONTHS | STATUS           |

|-----------------|-------------|---------------------------------|---------------------------|----------|--------------------|------------------|

| TSMC 5nm        | Client SoC  | ~ 75M gates, ~ 30 Blocks        | 15                        | Customer | 12                 | In Progress      |

| TSMC 6nm        | Client SoC  | ~ 190M gates, ~ 66 Blocks       | 35                        | Customer | 12                 | Taped-out        |

| TSMC 6nm        | Client SoC  | ~ 70M gates, 20 Blocks          | 15                        | Customer | 7                  | Taped-out        |

| TSMC 6nm        | GPU         | ~ 365M gates, ~ 100 Blocks      | 50                        | Customer | 11                 | In Progress      |

| TSMC 7nm        | GPU         | ~ 275Mgates, ~ 80 Blocks        | 44                        | Customer | 12                 | Functional       |

| TSMC 16nmFFP    | Video Game  | ~ 22M gates, 25 Blocks          | 10                        | Customer | 10                 | Production       |

| GF 14LLP        | Graphics    | ~ 40M gates, 30 blocks          | 11                        | Customer | 12                 | Production       |

| TSMC 28nm HPC+  | Networking  | ~ 103M gates, 14 Blocks         | 12                        | MosChip  | 15                 | Production       |

| TSMC 40nm G     | Networking  | ~ 12M gates, 8 Blocks           | 8                         | MosChip  | 7                  | Production       |

| GF 14nm HPP     | Ethernet    | ~ 28M gates, 9 Blocks           | 6                         | MosChip  | 7                  | Production       |

| TSMC 28nm HPC+  | GSP         | ~ 93M gates, 3 (Unique) Blocks  | 6                         | MosChip  | 12                 | Functional (PoC) |

| Samsung 14nmLPP | GSP         | ~ 120M gates, 3 (Unique) Blocks | 6                         | MosChip  | 12                 | Production       |

| TSMC 22nm ULL   | Edge SoC    | ~ 2.2M gates, Flat Chip         | 3                         | MosChip  | 4                  | Bring-up         |

# EMBEDDED SYSTEMS, SOFTWARE & PRODUCT DESIGN SERVICES

#### **OVERVIEW OF EMBEDDED GROUP**

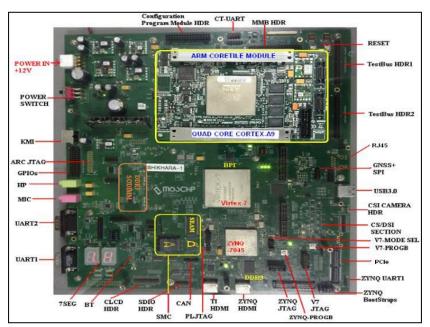

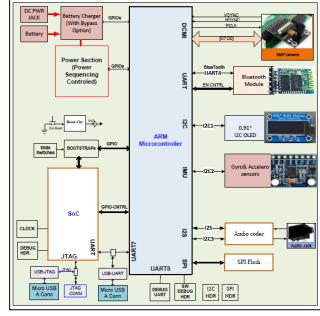

MosChip offers various Embedded Product Design Services such as:

- Embedded Product Design:

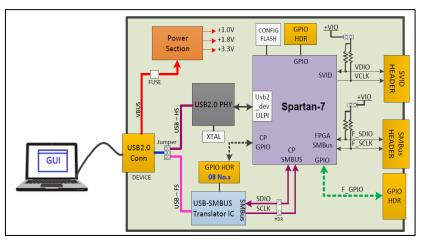

- Turn-key solutions with System Design, Software Development, FPGA Integration, Bring-up, Validation & Manufacturing / Production Enablement & Improvements, Formfactor Designs for Custom or COTS Enclosures

- Embedded System Software Development:

- BSP / OS Porting, Device Drivers, Integration, Bring-up, Validation & Maintenance with Version Control

- Complex & High-Speed System Design:

- System Architecture / Schematic Design, PCB Layout, SI / PI / Thermal Sims, Bring-up, Validation, Design updates with Version Control, Prototyping and Manufacturing

OS PORTING & BOARD SUPPORT PACKAGE (BSP)

**PROCESSORS**

Qualcomm

#### **400+ Engineers**

- 23+ Years Track Record with 500+ projects in Embedded Software Development & System Design

- Enabling solutions from Concept > POC > Production > Field Enablement

- Flexible engagement models in catering to Semiconductors, Defence, Medical, Storage, Computing, Consumer & IoT Product Segments

- Proven workflow of multiple designs with different Clients at different geo-graphic locations & product segments

- Engineering Partners for Indian Defence Labs

| MULTIMEDIA   | Display / Video / Audio Codecs & Controllers HDMI,<br>MIPI, CSI, DSI, Touch Screen, LCD/LVDS             |

|--------------|----------------------------------------------------------------------------------------------------------|

| PERIPHERALS  | DMA, I2C, I2S, McBSP, UART, MMC/SD, SPI, eMMC,<br>SDIO, NAND, NOR, DDR3/DDR4, PMIC & Power<br>Management |

| CONNECTIVITY | USB, PCI/PCIe, WLAN, IrDA ,Ethernet, ZigBee, BT/BLE,<br>GPS, NFC                                         |

#### **EMBEDDED SOFTWARE - SKILL SUMMARY**

| APPLICATIONS         | <ul> <li>GUI Design for Si Bring-up / Validation, Configuration &amp; Diagnostics</li> <li>Custom Applications – USB Over Ethernet, Serial Over Ethernet, NAS etc.,</li> <li>Low Level Firmware and Post</li> </ul>       |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MIDDLE WARE          | <ul> <li>Multimedia – Display, Audio / Video Codecs &amp; Controllers, HDMI, MIPI – CSI / DSI, Touch Screen, LCD/LVDS</li> <li>Power Management</li> <li>Connectivity - BT, WIFI, NFC, Zigbee &amp; GPS / GNSS</li> </ul> |

| SYSTEM<br>SOFTWARE   | <ul> <li>PBL, Uboot, XBL (UEFI), POST</li> <li>BSP, Board Bring-up</li> <li>Kernel &amp; Device Drivers (I2C, I2S, UART, MMC/SD, SPI, eMMC, SDIO, NAND, NOR, DDR, USB, PCI/PCIe, WLAN, Ethernet)</li> </ul>               |

| OPERATING<br>SYSTEMS | <ul> <li>Linux</li> <li>Android</li> <li>Windows</li> <li>RTOS – Vx Works, FreeRTOS</li> <li>Lattice SenseAI</li> <li>Arm Mbed</li> </ul>                                                                                 |

| PLATFORMS            | ARM, Freescale, TI, Samsung, Qualcomm, Xilinx, Lattice. Broadcom, Intel, Microchip Processors                                                                                                                             |

Multimedia Engineering

Al Engineering

Network Engineering

| FPGA DESIGN                                                                                                                                                                                                     | EMBEDDED SYSTEMS & SOFTWARE DEVELOPMENT                                                                                                                                                                                                            | SECURITY                                                                                                                                                                                                                                |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>RTL Front-End Design &amp; Integration</li> <li>FPGA Software &amp; Systems Bring-up</li> <li>FPGA Acceleration Solutions</li> <li>Interface &amp; IP Integration</li> <li>Reference Design</li> </ul> | <ul> <li>Platform Enablement</li> <li>Firmware &amp; Driver Development</li> <li>BSP &amp; Board Bring-up OS Porting &amp;<br/>Bootloader Optimization</li> <li>Middleware Integration</li> <li>Product Re-Engineering &amp; Sustenance</li> </ul> | <ul> <li>Secure Platform Root-of-Trust (PRoT)</li> <li>Fuzz &amp; Penetration Testing</li> <li>Edge to Cloud Security</li> <li>Device &amp; Data Security Lifecycle<br/>Management</li> <li>Identity &amp; Access Management</li> </ul> |

#### **Device Tools & Frameworks**

#### **Operating Systems**

#### Edge Tools & Frameworks

#### **AI ENGINEERING**

| COMPUTER VISION                                                                                                                                                                                                                                            | ML LIFECYCLE MANAGEMENT                                                                                                                                                                                                                                         | COGNITIVE COMPUTING                                                                                                                                                                                                                      | AI/FPGA ACCELERATION SOLUTIONS                                                                                                                                                                               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Machine &amp; Computer Vision Algorithms</li> <li>Object Detection, Identification &amp; Visual Perception</li> <li>Image Capture &amp; Optimization</li> <li>Vision Analytics &amp; Processing</li> <li>Optical Character Recognition</li> </ul> | <ul> <li>MLOps - Automated ML Pipeline<br/>Deployment</li> <li>Model Designing, Optimization,<br/>Testing &amp; Porting</li> <li>Inference Engines &amp; Metrics</li> <li>ML Transfer Learning Framework</li> <li>Data Augmentation &amp; Annotation</li> </ul> | <ul> <li>Deep Learning &amp; Neural<br/>Networks</li> <li>AI/ML on Edge &amp; Cloud</li> <li>ML Application Acceleration</li> <li>Cross Platform Porting &amp;<br/>Integration</li> <li>Natural Language<br/>Processing (NLP)</li> </ul> | <ul> <li>Scene Detection &amp; Text Analytics</li> <li>Predictive Analytics</li> <li>Audio Analytics &amp; Key-phrase Detection</li> <li>Face Recognition</li> <li>ML Reference Designs &amp; POC</li> </ul> |

#### Al Tools & Frameworks TensorFlow Lite **TensorFlow** Tesseract OCR K Keras spaCy O PyTorch XILINX VITIS kubernetes **Ö** Caffe2 Coral Edge TPU Compiler AWS DeepLens sens A AutoML LUIS Azure Machine Learning

#### **MULTIMEDIA ENGINEERING**

| AUDIO SOLUTIONS                                                                                                                                    | VIDEO SOLUTIONS                                                                                                                                                                  | EMBEDDED & MULTIMEDIA SYSTEMS                                                                                                                                                                                                                     | CAMERA ENABLED<br>SOLUTIONS                                                                                                                                                           | IMMERSIVE SOLUTIONS                                                                                                                                                             |

|----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Audio Codec Engineering</li> <li>Audio Command Detection</li> <li>Audio Algorithm Development</li> <li>ALSA Driver Development</li> </ul> | <ul> <li>Video Codec Engineering</li> <li>Surveillance &amp; DVR</li> <li>Video Analysis &amp; Validation</li> <li>VoD &amp; Media Streaming</li> <li>Image Stitching</li> </ul> | <ul> <li>Multimedia         Framework Integration</li> <li>Multimedia Systems &amp;         SDK Development</li> <li>Android Multimedia &amp;         HAL Development</li> <li>OpenVX Acceleration</li> <li>Media Infotainment Systems</li> </ul> | <ul> <li>Smart Camera<br/>Applications</li> <li>Firmware &amp; Driver<br/>Development</li> <li>Image Signal Processing<br/>(ISP)</li> <li>Camera Framework<br/>Integration</li> </ul> | <ul> <li>AR/VR application development</li> <li>VR gadget feature development</li> <li>VR streaming on Wi-Fi</li> <li>Open Standard based VR/AR</li> <li>VR on Cloud</li> </ul> |

#### Audio & Speech Codecs

**EVRC**

#### Video& Image Codecs

#### **Platforms**

#### **Architectures**

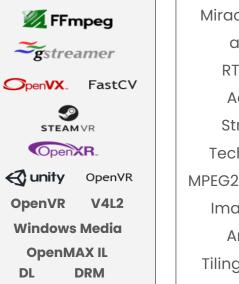

#### **Frameworks**

### Streaming & Screen-Casting

Miracast source

and sink

RTP | SRTP

Adaptive

Streaming

Technologies,

MPEG2 TS, WebRTC,

Image/Video

Analytics

Tiling | Stitching

#### **QUALITY ENGINEERING**

#### **QUALITY ASSURANCE & CERTIFICATION, COMPLIANCE & DEVICE & EMBEDDED TESTING DEVOPS & TEST AUTOMATION ML TESTING PRODUCT TESTING** CONSULTING · Multimedia, Audio/Video Performance & · Continuous Integration, FuSa - ISO 26262 Dataset & Feature Validation · Functional Testing Deployment & Testing Model Validation & Performance AUTOSAR & MISRA-C Testing Sensor Integration & Device to Cloud Benchmarking OpenVX Vision Library Embedded System Model Parameters Traceability & Integration Testing Interoperability Test Automation Conformance Tools/Frameworks ML Library Integration Testing Test Tool Development Peripherals & Test Automation Connectivity testing Network Interface Card Frameworks Embedded Neural Network Assessment & Integration Connected App/Edge • Automation Scripts **Application Testing** Validation Support CNN Compiler Validation · Feasibility Analysis Software Toolchain Testing • QA Farms Testing Test Lab Setup Advisory

Automation Frameworks

#### Version Control

#### Networking

#### In-House QA Tool

**TestNG**

STAF

#### **DIGITAL ENGINEERING**

| ЮТ                                                       | MOBILITY                                             | CLOUD                                               |

|----------------------------------------------------------|------------------------------------------------------|-----------------------------------------------------|

| IoT Device Connectivity                                  | Mobile App Development                               | Cloud Migration                                     |

| <ul> <li>Gateway Integration &amp; Management</li> </ul> | UX Design                                            | <ul> <li>Cloud Design &amp; Architecture</li> </ul> |

| Digital Twin                                             | <ul> <li>Mobile Test Automation Framework</li> </ul> | Cloud Service Integration                           |

| IoT Device Lifecycle Management                          |                                                      |                                                     |

| Gateway & Cloud Security                                 |                                                      |                                                     |

# Connectivity

#### Web/ Mobile Applications

#### Cloud

| WIRED                                    | WIRELESS                            |

|------------------------------------------|-------------------------------------|

| Network Protocol & App Development       | Wireless Solutions (Wi-Fi, BLE, RF) |

| Network Stack & Performance Optimization | Customer Premise Equipment          |

| Network Test Automation                  | WLAN Drivers                        |

| Network Module Integration               | Wi-Fi Co-existence                  |

| Software Defined Networking              |                                     |

#### Wired

#### Wireless

# SUMMARY OF RELEVANT SAMPLE EMBEDDED PROJECTS

| Application                     | Embedded Service                                                                                                      | Status    |

|---------------------------------|-----------------------------------------------------------------------------------------------------------------------|-----------|

| Home Automation                 | Firmware development of Wi-Fi module                                                                                  | Completed |

| Health Monitoring               | Firmware development of Wi-Fi & BLE MCU                                                                               | Completed |

| Autonomous Driving              | ECU software development<br>FuSA (ISO26262), MISRA-C Compliance                                                       | Completed |

| Multimedia                      | GStreamer plugins development & porting                                                                               | Completed |

| Multimedia                      | DSP based firmware development, audio codecs driver development                                                       | Completed |

| AIML                            | Data annotation, algorithm training, deployment Computer vision, NLP, OCR, NLP                                        | Completed |

| Multimedia                      | ALSA compliant Linux kernel audio driver, Audio firmware feature enhancement                                          | Completed |

| Camera                          | Profile & optimize low level u-boot code, A/V subsystem activation at boot-up, design & develop kernel wrapper module | Completed |

| Inertial Measurement Unit (IMU) | STM firmware development with peripherals like I2C, SPI, USB, etc.                                                    | Completed |

| Wireless                        | BT-Wi-Fi-LTE Co-existence IP firmware development & validation                                                        | Completed |

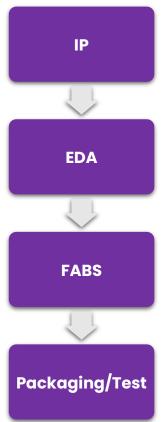

## SEMCIONDUCTOR TURNKEY ASIC

[RTL TO VOLUME PRODUCTION AND BRING-UP]

MICROCHIP

**RTL to Volume Production**

#### **TURNKEY ASIC**

**MO7CHIS**

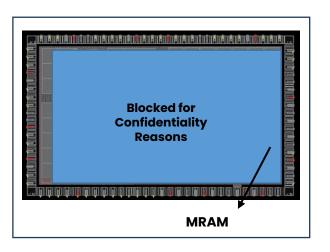

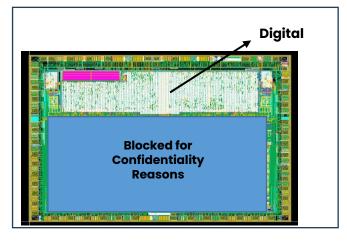

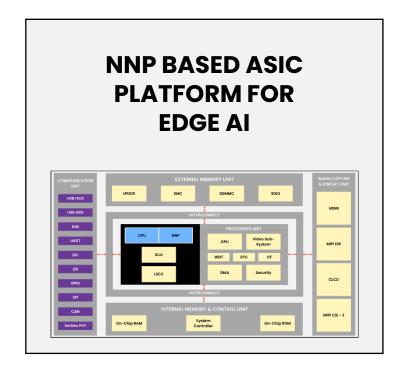

- Turnkey ASIC Edge SoC

- Turnkey Mixed Signal ASIC POWER IC

- Edge SoC Reference Platform & Bring-up

- Power IC Debug Platform Development

- Turnkey ASIC Matrix (Digital SoC)

- Matrix FPGA Platform Pre-Silicon Validation

- Matrix Reference Platform & BSP

# MosChip ASIC PLATFORMS

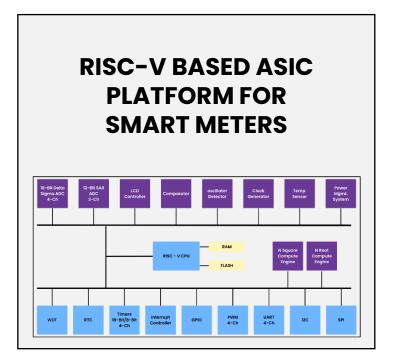

#### **MOSCHIP ASIC PLATFORMS**

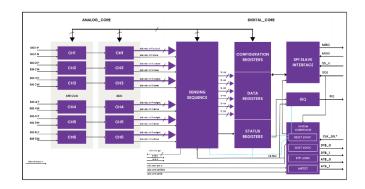

#### LOW FREQUENCY MONITORING ASIC PLATFORM FOR HEALTHCARE

### **THANK YOU**

#### HYDERABAD (HQ)

MosChip Technologies Limited 7th floor, My Home Twitza, TSIIC Hyderabad Knowledge City, Rangareddy – 500081, Telangana, India. Tel: +91-40-66229292

#### USA

MosChip Technologies, USA 4699 Old Ironsides dr Ste 270, Santa Clara, CA 95054 Tel: 408-737-7141

#### **BANGALORE**

MosChip Technologies Limited 03rd floor, Salarpuria Hallmark, outer ring road, Kadubeesanahalli, Bangalore – 560103, Karnataka, India Tel: +91-80-4146-3535

#### **AHMEDABAD**

Softnautics LLP

(A MosChip Company)

B block, 3rd floor, Westgate, sg

highway, Makarba,

Ahmedabad 380051, Gujarat

Tel: +91-79-35338580

#### PUNE

Softnautics LLP (A MosChip Company) 10th floor, Smartworks space, ap81, 83, n main road, near Hard Rock café, Mundhwa, Pune 411036, Maharashtra

**♡ ⊕ ⊕ ⊕ ⊘**/MosChipTech

Email: contact@moschip.com